# Muen System Specification

Adrian-Ken Rueegsegger, Reto Buerki

v0.7.2, April 9, 2024

無 緣

---

Copyright © 2024 codelabs GmbH

Copyright © 2024 secunet Security Networks AG

Further publications, reprints, duplications or recordings - no matter in which form, of the entire document or parts of it - are only permissible with the prior consent of codelabs GmbH or secunet Security Networks AG.

# Contents

|          |                                          |            |

|----------|------------------------------------------|------------|

| <b>1</b> | <b>Introduction</b>                      | <b>5</b>   |

| <b>2</b> | <b>System Policy</b>                     | <b>6</b>   |

| 2.1      | Policy Format . . . . .                  | 6          |

| <b>3</b> | <b>System Integration</b>                | <b>8</b>   |

| <b>4</b> | <b>Tau0 Concept</b>                      | <b>11</b>  |

| 4.1      | Static Mode of Operation . . . . .       | 11         |

| 4.2      | Dynamic . . . . .                        | 11         |

| <b>5</b> | <b>Toolchain</b>                         | <b>13</b>  |

| 5.1      | Overview . . . . .                       | 13         |

| 5.2      | Plugin System . . . . .                  | 16         |

| 5.3      | Core Tools . . . . .                     | 16         |

| 5.4      | Plugins . . . . .                        | 23         |

| 5.5      | Additional Tools . . . . .               | 24         |

| <b>6</b> | <b>Policy Validation</b>                 | <b>28</b>  |

| 6.1      | Configuration . . . . .                  | 28         |

| 6.2      | Devices . . . . .                        | 28         |

| 6.3      | Device Domains . . . . .                 | 29         |

| 6.4      | Events . . . . .                         | 29         |

| 6.5      | Files . . . . .                          | 30         |

| 6.6      | Hardware . . . . .                       | 30         |

| 6.7      | Kernel . . . . .                         | 31         |

| 6.8      | Memory . . . . .                         | 31         |

| 6.9      | Model Specific Registers (MSR) . . . . . | 33         |

| 6.10     | Platform . . . . .                       | 33         |

| 6.11     | Scheduling . . . . .                     | 33         |

| 6.12     | Subjects . . . . .                       | 34         |

| <b>7</b> | <b>Policy Structure</b>                  | <b>36</b>  |

| 7.1      | Policy Schema Documentation . . . . .    | 36         |

| <b>8</b> | <b>Appendix</b>                          | <b>105</b> |

| 8.1      | Annotated Example Policy . . . . .       | 105        |

| <b>9</b> | <b>Bibliography</b>                      | <b>143</b> |

# List of Figures

|                                  |    |

|----------------------------------|----|

| 3.1 System Integration . . . . . | 9  |

| 5.1 Build process . . . . .      | 27 |

# Listings

|     |                                   |     |

|-----|-----------------------------------|-----|

| 5.1 | $\tau_0$ Command Stream . . . . . | 20  |

| 8.1 | Demo System (VT-d) . . . . .      | 105 |

# Chapter 1

## Introduction

The Muen system policy is a description of a component-based system running on top of the Muen Separation Kernel (SK). It defines what hardware resources are present, how many active components (called subjects) the system is composed of, how they interact and which system resources they are allowed to access. The contents a Muen system policy is composed of are outlined in chapter 2.

A system integrator specifies and configures such a component-based system at integration time in XML format. The Muen toolchain transforms the system description in multiple steps to the final system description, resolving abstractions which exist to make life simpler and less error-prone to the integrator. Additionally, the toolchain also creates various build artifacts which are incorporated into the system image. Chapter 3 gives an overview of the system integration process.

The Muen SK can be regarded as a policy enforcement engine, in the sense that it has no knowledge about the actual content of the generated data structures and in consequence the policy. For example, it knows nothing about the contents of subject page tables which define a subject's address space, nor does it know anything about its own page tables. In fact, these structures are not even mapped into the kernel.

The most important and final step in the integration of a Muen system is the actual generation of the data structures which guarantee subject isolation and the composition of the final system image. This step is performed by a trusted system composer called (static)  $\tau_0$  (Tau Zero). The concept of  $\tau_0$  is introduced in chapter 4.

Section 5 explains every tool and the system image composer in detail. It also presents the usage of each tool. Section 6 then outlines all semantic checks performed on the system policy primarily by the validation tool, but also by other tools in the toolchain.

Finally section 7 specifies the XML schema and structure of the source format of the Muen system policy. Explanations and examples illustrate how to configure a component-based system with the Muen SK.

# Chapter 2

# System Policy

The Muen policy specifies the following properties of a system:

- Configuration values

- Hardware resources

- Platform description

- Physical memory regions

- Device domains

- Events

- Communication channels

- Components

- Subjects

- Scheduling plans

The policy serves as a static description of a Muen system. Since all aspects of the system are fixed at integration time the policy is very well suited for automated as well as manual validation prior to system execution.

The details of each property above is outlined with examples in the XSD-schema of the format source policy in section 7.

## 2.1 Policy Format

The system policy is specified in XML. There are currently three different main policy formats:

- Source Format

- Format A

- Format B

The motivation to have several policy formats is to provide abstractions and a compact way for users to specify a system in format source while simultaneously facilitate traceability as well as reduced complexity of tools operating on the policy formats A and B.

The implementation of such tools is simplified by the absence of higher-level abstractions in the latter formats which would make the extraction of input data more involved.

Furthermore, the final format B must specify every aspect of the system explicitly, e.g. all attributes have a concrete value assigned, something which would be very tedious and repetitive and that burden should not be put on an integrator.

The following sections give more detail about each policy format.

Only the policy in format source intended for system integrators is specified in this document. Other formats are processed by the toolchain and thus considered *internal*. While it is possible to specify a system policy in format A or B, it is not recommended.

Additionally to these three main formats, there may be extended versions of these formats if plugins are used. See section [5.2](#) for details about the plugin system.

### 2.1.1 Source Format

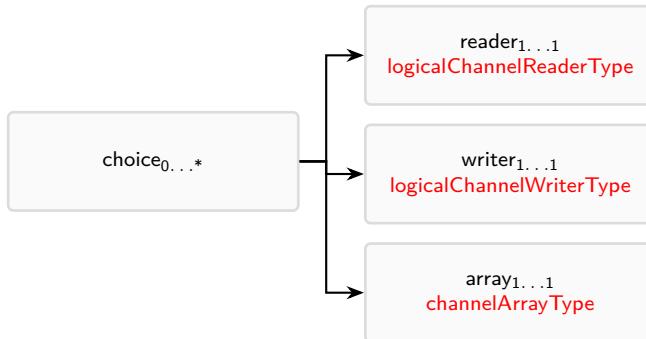

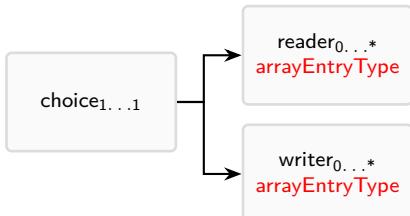

The user-specified policy is written in the so called *source format*. Constructs such as channels provide abstractions to simplify the specification of component-based systems. Many XML elements and attributes are optional and are *expanded* during later steps of the policy compilation process.

Kernel and  $\tau_0$  subject ([4.2](#)) resources are not part of the source format since they are automatically added as part of the policy expansion step.

The use of configuration values enables parametrization of the system policy.

The policy in source format is specified in detail in section [7](#), while appendix [8.1](#) provides an annotated example policy illustrating the various policy elements.

### 2.1.2 Format A

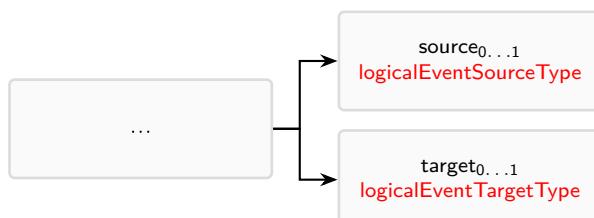

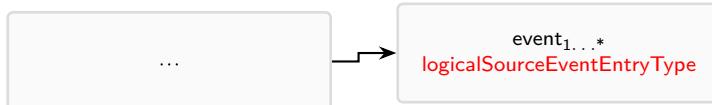

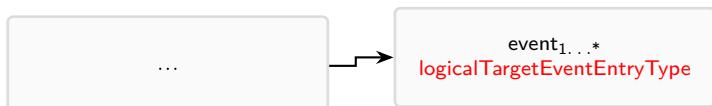

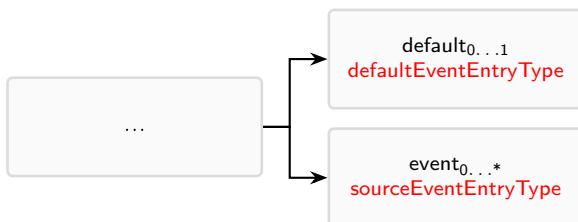

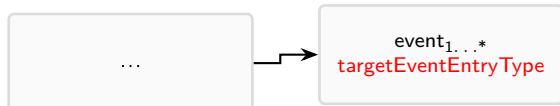

Format A is a processed version of the source format where all inclusions of external files are resolved and abstractions such as channels have been deconstructed into their constituent parts. For example, a channel is expanded to a physical memory region and the corresponding writer and reader subject mappings with the appropriate access rights. Optional associated events have been automatically created and correctly linked with the designated subjects.

In this format all implicit elements, such as for example automatically generated page table memory regions, are specified. The kernel and  $\tau_0$  configuration is also declared as part of format A.

The only optional attributes are addresses of physical memory regions.

### 2.1.3 Format B

Format B is equivalent to Format A except that all physical memory regions have a fixed location (i.e. their physical address is set).

# Chapter 3

# System Integration

A Muen system defined via the system policy is transformed and integrated by various tools to generate a bootable system image.

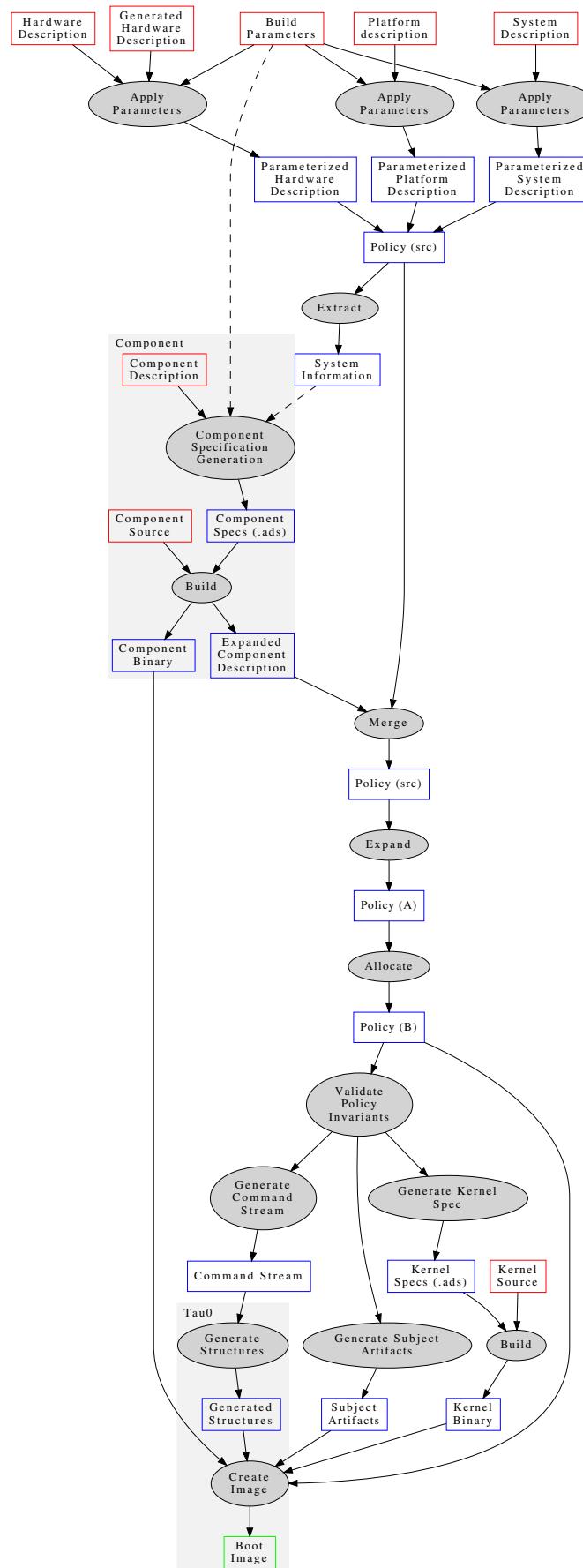

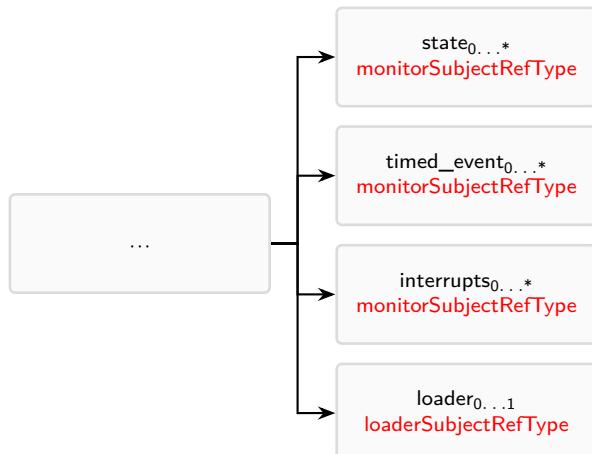

The directed graph 3.1 on page 9 illustrates the process.

At the top, the graph shows how configuration and build parameters are applied to the following constituents of the system policy:

- Hardware description (static)

Contains manually specified devices by the integrator, e.g. common hardware like I/O ports of a PC speaker. Such devices are not automatically collected by the hardware configuration generator.

- Hardware description (generated)

Hardware description extracted from a running Linux system by the `mugenhwcfg` tool (section 5.5.3).

- Platform description

Common names and abstractions to form a unifying view over different hardware configurations. Additionally, platform-specific configuration values can be provided here.

- System description

Specification of an actual component-based system running on the Muen SK.

These combined inputs form the parameterized system policy in format source, which can be used by components to extract system information. Such information might be for example the log channel count of a debug server subject, or whether a specific debug facility has been enabled by the system integrator.

The CSPECs mechanism outlined in the *Muen Component Specification* document [1] can be used by components to generate source specifications (e.g. in SPARK/Ada) from the component description. Furthermore, a component might expand its own component description with information extracted from system information, or it might use the `mucbinsplit` tool (section 5.5.4) to automatically fill in the memory regions provided by its binary after compilation. The expanded component description is then merged with the system policy for further processing.

After all component descriptions have been merged into the system policy, it is expanded by the expander tool (section 5.3.5). This step transforms the system policy from format source to format A. Abstractions like directed channels are now resolved to basic shared memory mechanisms and events, non-present optional attributes are added and set to default values.

The allocator tool (5.3.6) then loops over all physical memory regions which have no address assigned and places them in memory by allocating a region and thus a physical start address from the usable pool. The usable pool information is extracted from the allocatable memory block list (7.1.17) in the system policy. This process transforms the policy to format B where all elements must be present and attributes specified.

The policy is then checked for consistency and configuration errors by the validator tool (5.3.7). If a misconfiguration is found, the user is informed and the build aborts. The extensive checks performed by the validator tool are listed in section 6. If no error is found, the system policy is then ready to be used for three subsequent steps:

Figure 3.1: System Integration

- Generate kernel specifications (SPARK/Ada source files)

- Generate structures for subjects

- Create a command stream for  $\tau_0$

The kernel source specifications contain tables and constants which represent the policy that is compiled into the kernel as part of the kernel build process and enforced at runtime.

An example of generated subject structures are ACPI tables, which are mapped into a Linux VM to announce the available hardware resources.

The command stream generator (5.3.9) generates instructions in XML format for the  $\tau_0$  system composer explained in the following section.

# Chapter 4

## Tau0 Concept

The XML command stream together with the other build artifacts like subject structures or the kernel binary is provided as input to the trusted system composer  $\tau_0$ . Its task is to compose a system image while making sure that certain invariants are not violated. The  $\tau_0$  concept is a mechanism to gradually increase the flexibility of a component based system while keeping a high level of assurance regarding the correctness of isolation enforcement.

There are two modes of operation for  $\tau_0$ :

- static

- dynamic

In the static scenario, the task of  $\tau_0$  is to construct a bootable system image by assembling the input files and generating data structures such as page tables, all while checking that invariants necessary for correct isolation are valid. An example for such an invariant is that no subject memory mapping may reference a memory region containing paging structures.

For the dynamic case, the goal is to have a trusted  $\tau_0$  subject with additional privileges to interact with the Muen SK over a special  $\tau_0$  interface. This will allow  $\tau_0$  to change certain clearly defined aspects of the system state at runtime. A potential use-case would be to set up a new subject, assign resources like memory and devices to it and then instruct the kernel to schedule it.

Since it must be guaranteed that a dynamic system is as secure as the static one,  $\tau_0$  must be developed with the same care as the kernel itself, meaning it must be written in SPARK/Ada and security properties which provide hard isolation must be formally proven. This process is currently ongoing.

### 4.1 Static Mode of Operation

The static variant is the one which is currently implemented.  $\tau_0$  runs at integration time and assembles the system image by constructing the data structures guaranteeing isolation and merging in the build artifacts of the other Muen tools, like untrusted ACPI data structures for Linux VMs.

Static  $\tau_0$  fulfills its task by creating the system image in memory while processing the commands from the command stream. See listing 5.1 on page 20 for an example command stream.

$\tau_0$  is written in SPARK/Ada and it applies memory typization to formally prove aspects of the system. Command processing starts from a well-known good state and it is enforced that each system state transition resulting from a new command input results in a good state again by showing that invariants hold after the transition. If not, the command is rejected and the build aborts.

See the project README or the webpage<sup>1</sup> for more information about the current state of  $\tau_0$ .

### 4.2 Dynamic

While the system image is composed by the static variant of  $\tau_0$ , the goal is to run the same code as  $\tau_0$  subject at runtime. Note that this is not yet implemented but planned as a way

---

<sup>1</sup><https://muen.sk/tau0.html>

forward to achieve more dynamic systems while having the same assurance about security and safety properties.

The dynamic  $\tau_0$  running as subject will reconstruct the system state defined at integration time and continue to process commands starting from there. Depending on the system use case, commands might be sent to dynamic  $\tau_0$  by a special control subject.

The dynamic variant can be divided into multiple sub-variants, depending on how much dynamic system behavior is allowed. For example, the initial dynamic variant might only allow entity construction, not destruction.

# Chapter 5

# Toolchain

## 5.1 Overview

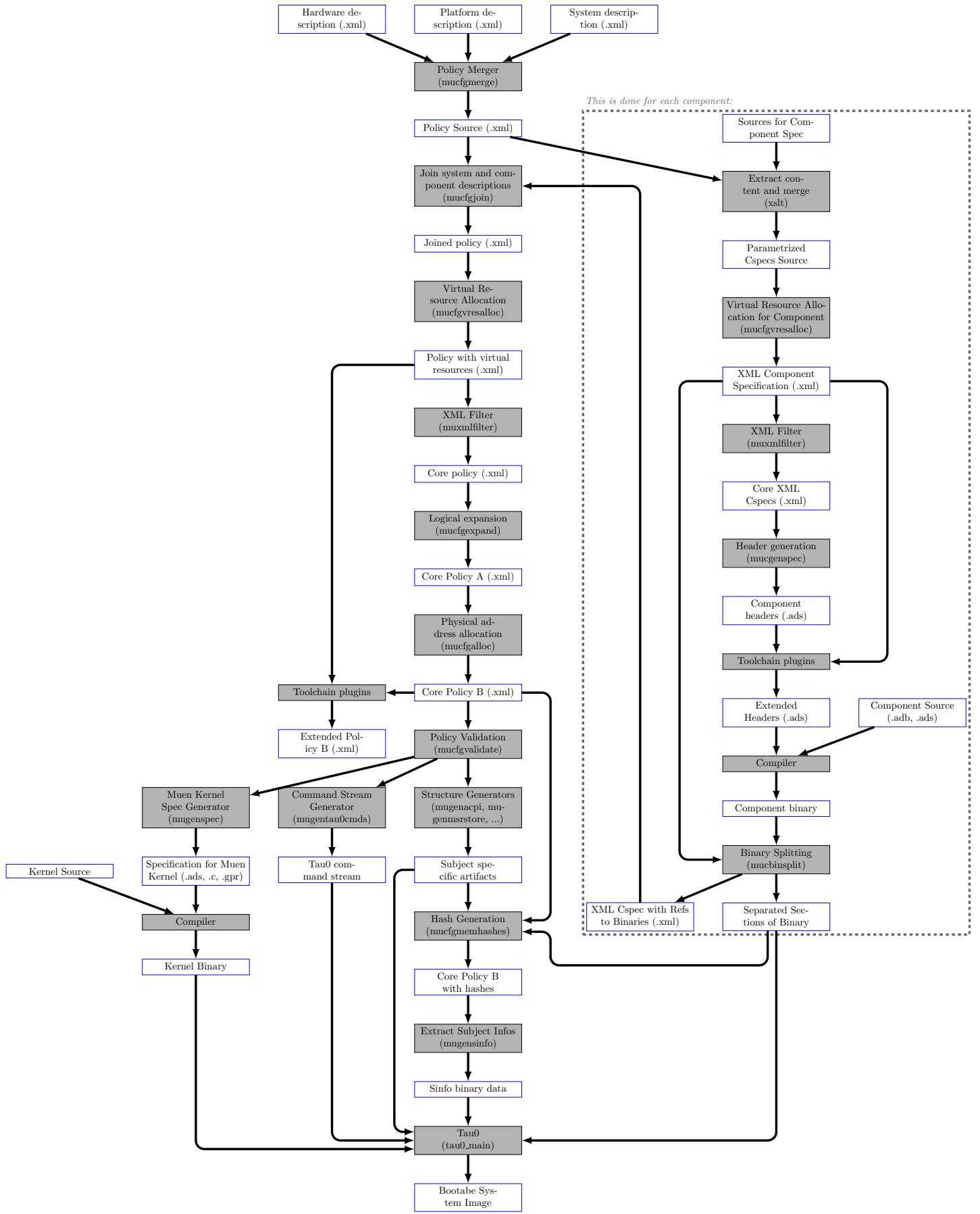

While the previous section 3 presented an overview of the system integration process and section 4 introduced the  $\tau_0$  concept, this section focuses on the detailed description of the tools forming the Muen toolchain.

The tool-based processing of the Muen system policy can be divided into the following steps:

- Policy merging

- Components build

- Components specification merging

- Policy compilation

- Policy validation

- Structure generation

- Command stream generation for  $\tau_0$

- Image generation by  $\tau_0$

Following the Unix philosophy "A program should do only one thing and do it well" each of the tools only performs a specific task. They work in conjunction to process a user-defined policy and build a bootable system image. Figure 5.1 presents another illustration of the policy processing, this time laying the focus on the tools. The following sections explain each processing step while section 5.3 describes each tool separately.

### 5.1.1 Policy Merging

The Merger tool outlined in section 5.3.3 is responsible to merge XML files stored at different locations on the file system into one system policy in format source.

The tool reads a system configuration in XML format to locate the following files:

- System policy

- Hardware specification

- Additional hardware specification

- Platform specification

To make the system description flexible and modular the following features are supported in the input policy:

- The tool provides an implementation of the XML XInclude mechanism<sup>1</sup>. Using includes, the policy writer is able to separate and organize the system policy as desired. Instead of specifying the whole policy in one file, the subject specifications can be split into separate files, or common parts shared by different system descriptions can be extracted.

- Expressions can be used to formulate (nested) terms using equality/inequality, numeric and logical operators as well as concatenation of strings. Expressions can be used just like configuration variables to provide parameters for other mechanisms.

- The use of conditionals enables selective activation of parts of the source policy depending on the value of a given configuration variable. This allows flexible customization of a system during policy compilation by setting the value of a configuration variable or formulating an appropriate expression.

- Configuration variable substitution enables the policy writer to set the value of attributes to those of referenced configuration variables or expressions. Attributes that start with a dollar sign followed by a variable name are substituted by the value of the variable.

- The policy may define templates for XML code, including parameters that can be used within expressions, conditionals and references within that template. Templates can be employed to avoid code duplication and to encapsulate portions of code. Hence, templates can define building blocks and help to provide a high-level view of a system.

- When two building blocks are connected via a channel or when a subject behaves like a client of another subject, it is desirable to insert a communication channel into a subject from “outside” of that subject. Such additions to an XML node are possible with amend statements. On evaluation, the children of an amend-node are merged into the children of the node specified by the given XPath.

After the merge step, the resulting policy is well formatted to minimize the difference in the generated policies resulting from the subsequent tasks. This allows the user to easily review (`diff`) and therefore verify the results of each policy compilation task.

### 5.1.2 Components Build

After hardware, platform and high-level system policy are merged into a single source policy file, components may extract relevant information. For example an XSL transformation (XSLT) script could extract the I/O port of a specific device and create a corresponding configuration value based on it, which is then included in the component specification.

The `mucfgcvresalloc` tool described in 5.3.1 implements the blue *Component VR Allocator* task shown in figure 5.1. It is primarily used to automatically allocate attributes of component resources like *virtualAddress* for channels. Furthermore, similar to the policy merger, it supports inclusions, conditionals, expressions and configuration value substitutions.

After the component specification has been processed, the `mucgenspec` tool described in 5.3.11 generates Ada/SPARK packages containing constants derived from the declared component resources and config values. These constants can be used to reliably address specific or configurable resources in the source code. With these constants the component source code is compiled into a binary.

The `mucbinsplit` tool described in 5.5.4 can be used to extract ELF sections of the component binary into separate files. It automatically extends the component specification by adding a corresponding memory region with the appropriate access rights (e.g. executable, writable) for text, rodata, data, bss and stack sections.

### 5.1.3 Components Specification Merging

The processed component specifications are merged into the system source policy by the Muen component specification joiner tool described in section 5.3.4.

This step is optional as static component specifications which need no processing can also be manually specified in the system policy directly.

---

<sup>1</sup><http://www.w3.org/TR/xinclude-11/>

### 5.1.4 Policy Compilation

Policy compilation encompasses the tasks involved to transform the policy from source format to format A and finally to format B, which is the fully expanded format with no implicit properties.

The Virtual Resource Allocator tool sets virtual resources that are left unassigned in the joined policy. These resources include virtual addresses, event numbers and vectors of channels. Often, the precise values of these resources do not matter to the integrator and make the policy harder to read and write. Section 5.3.2 explains the Virtual Resource Allocator tool in detail.

The Expander tool takes care of completing the user-specified policy with additional information and resolving abstractions only available in format source to their corresponding low-level constructs.

For example, the concept of *channels* only exists in format source. Therefore a channel specified in format source must be expanded to shared memory regions with optional associated events in format A. Also, the Expander tool inserts specifications for the Muen kernel itself so the user is lifted from that burden. Generally, the aim of the expansion task is to make the life of a policy writer as easy as possible by expanding all information which can be derived automatically. Section 5.3.5 explains the Expander tool in detail.

The result of the expansion task is a policy in format A which is the input for the Allocator tool. This tool is responsible to assign physical memory addresses to all memory regions which are not already explicitly placed in memory. By querying the hardware section of the policy, the tool is aware of the total amount of available RAM on a specific system and allocates regions of it for memory elements with no explicit physical address. The Allocator tool also implements optimization strategies to keep the resulting system image as small as possible. For example, file-backed memory regions (e.g. a memory region storing a component executable) are preferably placed in lower physical regions. See section 5.3.6 for a description of the Allocator tool.

After the allocation task is complete, the policy is stored in format B. This format states all system properties explicitly and is used as input for the Validation step.

### 5.1.5 Policy Validation

Before structures required to pack the final system image are generated, the policy must be thoroughly validated to catch errors in the system specification. Such errors might range from overlapping memory, undefined resource references to incomplete scheduling plans etc. The Validator task performs checks that assure the policy in format B is sound and free from higher-level errors that are not covered by XML schemata restrictions.

It is important to always run the Validator as the system could otherwise exhibit unexpected behavior. This is especially true if a policy writer decides to specify the system directly in format B which is also possible but not advised. Section 5.3.7 explains the usage of the Validator tool, while section 6 outlines all performed checks.

It should be noted that correct memory typization and all invariants enforced by  $\tau 0$  when constructing the system image cannot be bypassed, since the checks are inherent to the generation of the bootable image file.

### 5.1.6 Structure Generation

The structure generation step encompasses various tools which extract information from a policy in format B and generate files in different formats.

While some generated files are directly linked into the Muen kernel (i.e. Source Specifications, see 5.3.11), most of them are subject-related. Depending on the subjects included in the actual system policy, the following subject structures are generated:

- MSR store regions

- Sinfo regions

- Regions for Linux VMs

- ACPI tables

- Linux zero-page (ZP) regions

- Regions for MirageOS/Solo5<sup>2</sup> unikernels

- Solo5 boot info

As these structures do not affect isolation between subjects or subjects and the kernel, they are not generated by  $\tau_0$  but only included as binary data via XML command stream and build artifacts.

The structure generator tools are explained in section [5.3.11](#).

### 5.1.7 Image Creation

The system image composer assembles the final system image. This task is performed by  $\tau_0$  static introduced in the previous section [4.1](#). The usage of it is specified in [5.3.10](#).

## 5.2 Plugin System

As is shown in figure [5.1](#), the build process includes two steps where plugins may be inserted if needed. The intention of the plugin system is to simplify the introduction of small, less critical modifications to the toolchain and keep those separate from the “core”-toolchain of Muen. A tool is considered to be part of the core-toolchain if it is *needed* to build the bootable system image. Additionally, `Mucfgvalidate` is considered part of the core-toolchain, too.

An example of a plugin is the documentation-plugin (see [5.4.2](#)). It can help to build documentation for a system and the user can easily adjust its functionality and the underlying XSD-schema as needed. Similarly, a plugin can be used to extend the automatically generated headers of components.

To hide the additional information in the policy from tools that may not be able to digest them, `mxmxmlfilter` (see [5.4.1](#)) is used to remove such parts of the policy before processing it. That way, changes in the plugins have minimal impact on the core toolchain.

To enable the validation of extended policies, the plugin system includes tools that extend policy format definitions. Hence, there may be extended versions of Source Format, Format A and Format B, depending on plugin usage.

## 5.3 Core Tools

This section describes the tools which form the core of the Muen toolchain.

### 5.3.1 Component Virtual Resource Allocator

The tool `mucfgcvresalloc` processes a user provided component specification and outputs a finished, schema compliant description of the component interface. Just like `mucfgmerge` it supports inclusion of external files, conditionals, expressions and substitutions. Furthermore, it can automatically allocate virtual resources as described below.

#### Name

`mucfgcvresalloc`

#### Input

Component configuration as XML, colon-separated list of include paths

#### Output

Component specification as XML in component format

The main processing steps are:

1. Merge XIncludes of main XML file, i.e., insert the referenced files at the given location;

2. Evaluate expressions, conditionals and substitutions;

3. Assign missing virtual addresses of channels and memory regions, as well as arrays of channels and memory regions;

---

<sup>2</sup><https://github.com/Solo5/solo5>

4. Assign missing IRQs of channel reader events and arrays of channel readers;

5. Assign missing event IDs of channel writer events and arrays of channel writers;

Virtual addresses, IRQs and event IDs are considered to be *virtual resources*. Each of the three virtual resources has its own domain. To request automatic allocation of the attribute `virtualAddress` (or `virtualAddressBase` for arrays) omit the attribute. To request automatic allocation of event ids of readers or writers the respective attribute must be set to `auto`.

To determine which addresses or ids to choose, `mucfgvresalloc` looks at the addresses and ids already present in the file. Dependencies of virtual resources through libraries or the system policy can be resolved by manually assigning such resources.

### 5.3.2 Virtual Resource Allocator

The tool `mucfgvresalloc` processes the joined system policy and outputs a system policy in format source. Its purpose is to automatically allocate virtual resources within subject descriptions.

**Name**

`mucfgvresalloc`

**Input**

Joined system policy as XML

**Output**

System policy where all virtual resources of subjects have been assigned

`mucfgvresalloc` can assign virtual addresses of channels and memory regions, IRQs of channel reader events, and IDs of channel writer events. These attributes are considered to be *virtual resources*. Each of the three virtual resources has its own domain. To request automatic allocation of the attribute `virtualAddress` omit the attribute. For the other two resources the respective attribute must be set to `auto`.

To determine which value to choose for a virtual resource, `mucfgvresalloc` processes each subject separately. For each subject, it gathers virtual resources already set in the component that is referenced by the subject and resources set in the subject itself. Thereafter, missing virtual resources are either set to the value fixed by the component (if possible) or chosen from the remaining space in the respective domain.

Dependencies of virtual resources through libraries or devices can be resolved by manually assigning such resources.

### 5.3.3 Policy Merger

The merger tool `mucfgmerge` combines user-provided system policy files into a single XML document.

**Name**

`mucfgmerge`

**Input**

System configuration as XML, colon-separated list of include paths

**Output**

System policy in format source (merged)

This tool reads the system configuration and merges the specified system policy, hardware and platform files into a single file. To ease the creation of many similar variants of a system the provided system policy may use templates, expressions, conditionals and amend statements. The main processing-steps are:

1. Merge XIIncludes of system policy into the system policy, i.e., insert the referenced files at the given location;

2. Merge hardware, additional hardware and platform specifications into the system policy. This includes merging the platform configuration section into the global configuration section;

3. Instantiate the templates, using the provided values and variable names;

4. Evaluate expressions, resulting in new configuration variables;

5. Replace all references to configuration variables with their value;

6. Evaluate conditionals, i.e., decide which sub-trees of the XML-tree to discard;

7. Evaluate amend statements, i.e., move sub-trees within the XML-tree.

The result is in policy source format and re-formatted so changes to the policy by subsequent build steps can be manually reviewed or visualized by diffing the files. In particular, the result does not contain any templates, expressions, conditionals or amend statements. The tool has debug modes that increase the verbosity of the output, in particular in case of errors.

#### 5.3.4 Component Specification Joiner

The Muen component specification joiner adds component XML specifications to the component section of a specified system policy and writes the result to a designated output file. Each given component/library specification is loaded and validated against the component specification XML schema. If it is correct the content is added to the components section of the system policy specified as input file. If the given system policy does not yet contain a components section, it is created. The result is written to the file specified by the `-o` parameter. In-place processing is supported by passing in the same value for input and output file.

**Name**

`mucfgcjoin`

**Input**

System policy in format source, comma-separated list of component specs

**Output**

System policy in format source (joined)

#### 5.3.5 Expander

The expander completes the user-provided system policy by creating or deriving additional configuration elements.

**Name**

`mucfgexpand`

**Input**

System policy in format source

**Output**

System policy in format A (expanded)

The Expander performs the following actions:

- Pre-check the system policy to make sure it is sound

- Expand channels

- Expand device resources

- Expand device isolation domains

- Expand kernel sections

- Expand minimal  $\tau_0$  subject

- Expand additional memory regions

- Expand hardware-/platform-related information

- Expand additional subject information

- Expand profile-specific information

- Expand scheduling information

- Post-check resulting policy

### 5.3.6 Allocator

The Allocator is responsible to assign a physical address to all global memory regions.

**Name**

mucfgalloc

**Input**

System policy in format A

**Output**

System policy in format B (allocated)

First, the Allocator initializes the physical memory view of the system based on the physical memory blocks specified in the XML hardware section. It then reserves memory that is occupied by pre-allocated memory elements (i.e. memory regions with a physical address or device memory). Finally it places all remaining memory regions in physical memory. In order to reduce the size of the final system image file-backed memory regions are placed at the start of memory.

### 5.3.7 Validator

The Validator performs additional checks that go beyond the basic restrictions imposed by the XML schema validation. For example it checks that the hardware provides an IOMMU device and that all references to subjects are resolvable. See [6](#) for a complete list of all executed checks. The tool aborts with a non-zero exit status and an explanatory message to the user if checks fail.

**Name**

mucfgvalidate

**Input**

System policy in format B

**Output**

None, raises exception on error

### 5.3.8 Hasher

The mucfgmemhashes tool is used to add memory integrity hashes to a given policy.

**Name**

mucfgmemhashes

**Input**

System policy in format B, colon-separated list of input directories containing build artifacts

**Output**

System policy in format B with memory integrity hashes

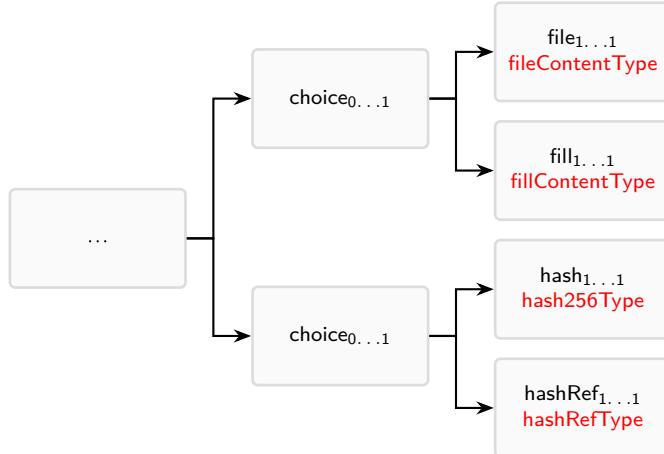

The tool appends a hash to all memory regions with fill and file content. It must run after all files have been generated by the structure generator tools.

The actual hash is generated using the SHA-256 algorithm and is intended to be used to verify the integrity of memory regions during runtime.

Note that no hashes are generated for sinfo memory regions. Since the hash information is exported via sinfo, and the sinfo region is itself part of the memory information of a subject, this hash would be self-referential.

The tool also replaces all occurrences of hashRef elements. A hash reference element instructs the tool to copy the hash element of the referenced memory region after message digest generation.

From an abstract point of view, the hashRef element is a way to link multiple memory regions by declaring that the hash of the content is the same. The hash may serve as an indicator on how to reconstruct the (initial) content of a memory region. This mechanism is used by e.g. the subject loader (SL) during subject init and reset operation. The subject loader expansion step remaps writable memory regions of the loadee (the subject under loader control) to SL and replaces the original regions with new ones containing a hash reference to the associated physical memory region. This way SL is able to determine the intended content of the target memory region by looking up the region in its sinfo page using the hash value as key.

### 5.3.9 Tau0 Command Stream Generator

The mugentau0cmds tool creates an XML command stream for  $\tau_0$  to let it compose the system image specified by the system policy given as input.

The tool reads the policy in format B and translates it to a sequence of commands as shown in the following listing:

```

1  <tau0>

2    <commands>

3      <addMemoryBlock address="16#0000#" size="157"/>

4      <addMemoryBlock address="16#0010_0000#" size="130816"/>

5      <addMemoryBlock address="16#2020_0000#" size="130564"/>

6      <addMemoryBlock address="16#4000_5000#" size="453932"/>

7      <addMemoryBlock address="16#bae9_f000#" size="256"/>

8      <addMemoryBlock address="16#baf9_f000#" size="96"/>

9      <addMemoryBlock address="16#0001_0000_0000#" size="3401216"/>

10     <addMemoryBlock address="16#ba3b_a000#" size="23"/>

11     <addMemoryBlock address="16#bb80_0000#" size="16896"/>

12     <addProcessor id="0" apicId="0"/>

13     <addProcessor id="1" apicId="2"/>

14     <addIoapic sid="16#f0e8#/"/>

15     <createLegacyDevice device="0"/>

16     <addIOPortRangeDevice device="0" from="16#03c0#" to="16#03df#"/>

17     <addMemoryDevice device="0" caching="WC" address="16#000a_0000#" size="32"/>

18     <activateDevice device="0"/>

19     <createLegacyDevice device="1"/>

20     <addIOPortRangeDevice device="1" from="16#0060#" to="16#0060#"/>

21     <addIOPortRangeDevice device="1" from="16#0064#" to="16#0064#"/>

22     <addIRQDevice device="1" irq="1"/>

23     <addIRQDevice device="1" irq="12"/>

24     <activateDevice device="1"/>

25     <createLegacyDevice device="2"/>

26     <addIOPortRangeDevice device="2" from="16#0070#" to="16#0071#"/>

27     <activateDevice device="2"/>

28     <createLegacyDevice device="3"/>

29     <addIOPortRangeDevice device="3" from="16#0cf9#" to="16#0cf9#"/>

30     <addIOPortRangeDevice device="3" from="16#0404#" to="16#0404#"/>

31     <activateDevice device="3"/>

32     <createLegacyDevice device="4"/>

33     <addMemoryDevice device="4" caching="UC" address="16#fec0_0000#" size="1"/>

34     <activateDevice device="4"/>

```

Listing 5.1:  $\tau_0$  Command Stream

As  $\tau_0$  strictly enforces certain invariants, the system must be constructed in a way not to violate these invariants. For example, before memory can be typed as being a VT-d root table, this memory must be cleared. Otherwise the memory typing model of  $\tau_0$  is violated.

The mugentau0cmds tool must take this into consideration when iterating over the resources specified in the input system policy and generating commands which instruct  $\tau_0$  to create the specified system.

**Name**

mugentau0cmds

**Input**

System policy in format B

**Output**

XML command stream for  $\tau_0$  static

### 5.3.10 Tau0 Static

The  $\tau_0$  static component serves as an image composer during integration. The concept and motivation of this approach is described in chapter 4.

**Name**

tau0\_main

**Input**

XML command stream, colon-separated list of input directories containing build artifacts

**Output**

Muen system image

**Output format**

Command Stream Loader (CSL) image<sup>3</sup>, bootable by any compliant bootloader.

<sup>3</sup><https://www.codelabs.ch/download/bsbsc-spec.pdf>

If a command is received which violates a constraint enforced by  $\tau_0$  static, the tool aborts system image construction, displays an error message and returns with a non-zero exit status.

### 5.3.11 Structure Generators

These tools do not change the policy and use it read-only.

#### MSR Stores Generator

Generate MSR store for each subject with MSR access.

##### Name

`mugenmsrstore`

##### Input

System policy in format B

##### Output

MSR store files of subjects in binary format

##### Output format

Intel SDM Vol. 3C, "24.8.2 VM-Entry Controls for MSRs" and Intel SDM Vol. 3C, "24.7.2 VM-Exit Controls for MSRs".

The tool generates MSR stores for each subject. The MSR store is used to save/load MSR values of registers not implicitly handled by hardware on subject exit/resumption.

MSR stores are used by hardware (VT-x) to enforce isolation of MSR (i.e. subjects that have access to the same MSRs cannot transfer data via these registers).

#### ACPI Tables

Generate ACPI tables for all Linux subjects.

##### Name

`mugenacpi`

##### Input

System policy in format B

##### Output

ACPI tables of all Linux subjects

##### Output format

Advanced Configuration and Power Interface (ACPI) Specification<sup>4</sup>

ACPI tables are used to announce available hardware to VM subjects. A set of tables consists of an RSDP, XSDT, FADT and DSDT table. See the ACPI specification for more information about a specific table.

#### Linux Zero Pages

Generate Zero Pages for all Linux subjects.

##### Name

`mugenzp`

##### Input

System policy in format B

##### Output

Zero pages of all Linux subjects

##### Output format

Linux Boot Protocol<sup>5</sup>

Zero Page<sup>6</sup>

<sup>4</sup><http://www.acpi.info/DOWNLOADS/ACPIspec50.pdf>

<sup>5</sup><https://www.kernel.org/doc/Documentation/x86/boot.txt>

<sup>6</sup><https://www.kernel.org/doc/Documentation/x86/zero-page.txt>

The so-called Zero Page (ZP) exports information required by the boot protocol of the Linux kernel on the x86 architecture. The kernel uses the provided information to retrieve settings about its runtime environment:

- Type of bootloader

- Map of physical memory (e820 map)

- Address and size of initial ramdisk(s)

- Kernel command line parameters

## Solo5 Boot Info

Generate Solo5 boot info structures for MirageOS unikernels<sup>7</sup> running on the Solo5 platform.

### Name

`mugensolo5`

### Input

System policy in format B

### Output

Solo5 boot info for all MirageOS subjects

### Output format

`struct hvt_boot_info`<sup>8</sup>

The boot info structure exports information required by Solo5. The unikernel uses the provided information to retrieve settings about its runtime environment:

- Memory size in bytes

- Address of end of unikernel

- CPU cycle counter frequency, Hz

- Address of command line (C string)

- Address of application manifest

## Kernel Source Specifications

Generate source specifications used by kernel.

### Name

`mugenspec`

### Input

System policy in format B

### Output

Source specifications in SPARK, C and GPR format

Gathers data from the system policy to generate various source files in SPARK, C and GNAT project file (GPR) format. Created output includes constant values for memory addresses, device resources, scheduling plans, etc. See the description of the `Skp` package hierarchy in the Muen Kernel Specification document [2] for the exact information these packages provide.

---

<sup>7</sup><https://mirage.io>

<sup>8</sup>[https://github.com/Solo5/solo5/blob/master/include/solo5/hvt\\_abi.h](https://github.com/Solo5/solo5/blob/master/include/solo5/hvt_abi.h)

## Component Source Specifications

Process component description and generate source specifications from it.

### Name

`mucgenspec`

### Input

Component description in XML

### Output

Component source specifications in SPARK

The component spec generation tool generates Ada/SPARK packages containing constants of the declared logical component resources. The generated specifications can be used in the component source code to access the declared resources.

## Subject Info (sinfo)

Generate subject information data for each subject.

### Name

`mugensinfo`

### Input

System policy in format B

### Output

Subject info data in binary format

### Output format

As specified in [1] and `common/musinfo/musinfo.ads`

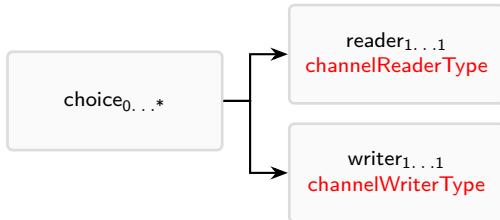

The Sinfo page is used to export subject information data extracted from the system policy to subjects. Currently, information about available memory regions, communication channels, events, vectors and assigned PCI devices is provided.

## 5.4 Plugins

This section lists tools which are either plugins for the toolchain or support the plugin system.

### 5.4.1 XML Filtering

The `muxmlfilter` tool can filter a given XML-file such that the output satisfies a given schema definition.

### Name

`muxmlfilter`

### Input

XSD-Schema, XML-file

### Output

Filtered XML-file where all nodes not allowed by the given schema have been deleted

The filter is intended for XML files that satisfy the target schema, except for some added element-nodes that are not allowed by the schema. The possibility to filter out some elements is needed to make toolchain-plugins possible (see 5.2).

The given schema can either be one of the built-in schemata (in which case it can be given by name), or it can be specified by a file-path. While `muxmlfilter` is not specific to Muen policies, the used schema needs to satisfy a number of technical restrictions. These are described in `tools/libmuxml/schema_plugins/README.md`

### 5.4.2 Documentation Transfer

The `doc_transfer` script can extend a given policy B with documentation nodes.

#### Name

`doc_transfer`

#### Input

Policy B XML-file, joined policy XML-file

#### Output

Policy B with added documentation

The tool processes the given joined policy and extracts a list of target XPath-addresses paired with an XML-node containing documentation. This list is then applied to the given policy B, which effectively transfers documentation from the given joined policy to the given policy B. This way, documentation information that was present in policy src can be reinserted in policy B. The amended policy B can serve as a single source for documentation information.

## 5.5 Additional Tools

This section lists additional helper tools which simplify the process of generating and validating a Muen system.

### 5.5.1 Kernel ELF Checker

The `muchekelf` tool enforces that the format of a given Muen kernel ELF binary matches the kernel memory layout specified in a system policy. Furthermore, the ELF kernel entry point is compared to the expected value.

Size, VMA (Virtual Memory Address) and permissions of binary ELF sections are validated against kernel memory regions defined in the policy. The following table lists the correspondence of ELF section names to logical kernel memory region names.

| ELF Section              | Memory Name                     |

|--------------------------|---------------------------------|

| <code>.text</code>       | <code>kernel_text</code>        |

| <code>.data</code>       | <code>kernel_data</code>        |

| <code>.rodata</code>     | <code>kernel_ro</code>          |

| <code>.bss</code>        | <code>kernel_bss</code>         |

| <code>.globaldata</code> | <code>kernel_global_data</code> |

### 5.5.2 Stack Usage Checker

The `muchekstack` tool statically calculates the worst-case stack usage of a native Ada/SPARK component or the Muen kernel compiled with the `-fcallgraph-info` switch<sup>9</sup>.

The tool takes a GNAT project file and a stack limit in bytes as input. All control-flow information (.ci) files found in the object directory of the main project and all of its dependencies are parsed. Once the control-flow graph is constructed the maximum stack usage of each subprogram is calculated and checked against the user-specified limit. The tool exits with a failure if a stack usage exceeding the limit is detected.

Note that the tool is not applicable to arbitrary software projects as it does not handle dynamic/unbounded stack usage and recursion. In the context of the Muen project these cases can not occur since they are prohibited by the following restriction pragmas:

- `No_Recursion`

- `No_Secondary_Stack`

- `No_Implicit_Dynamic_Code`

Additionally, the `-Wstack-usage` compiler switch warns about potential unbounded stack usage.

<sup>9</sup>[https://www.adacore.com/uploads/technical-papers/Stack\\_Analysis.pdf](https://www.adacore.com/uploads/technical-papers/Stack_Analysis.pdf)

### 5.5.3 Hardware Config Generator

The mugenhwcfg<sup>10</sup> tool has been created to automate the process of gathering all necessary hardware information. To collect data for a new target hardware all that is required is to run the tool on a common Linux distribution<sup>11</sup>. See the project README for more information.

**Name**

mugenhwcfg

**Input**

*None*

**Output**

Hardware description in `output.xml`

The tool is implemented in a way to extract as much information from the system and generate a hardware configuration even if problems are encountered. The aim is to assist the integrator as much as possible in writing a hardware configuration for the target hardware.

Therefore, the tool only fails with a non-zero exit status and no output if essential required data can not be extracted from the system. Other problems are reported in the potentially incomplete `output.xml` file as XML comments, making the encountered problems on the actual machine evident. The following snippet provides an example of such a warning comment in the header of the generated `output.xml` file:

```

* WARNING *: Unable to resolve device class 0c80. Please update pci.ids

(-u) and try again

```

The comments should be rather self-explanatory. In this case, the problem is only a minor issue since the tool was simply unable to resolve a device class number to a human-readable string.

The next example has more consequences:

```

* WARNING *: Skipping invalid IRQ resource for device 0000:00:1f.3: None

```

This has the effect that no IRQ resource is appended in the specification of the device exhibiting this problem. While the device can still be assigned to a subject, it is missing the IRQ element and as a result the IRQ resource itself. It can be assumed that this leads to problems with the driver interacting with the device. For proper operation, it is the policy writer's task to rectify the hardware specification by determining the correct configuration manually.

### 5.5.4 Component Binary Splitter

The mucbinsplit tool splits component binaries into multiple files, one per ELF section.

**Name**

mucbinsplit

**Input**

Component description in XML, Component ELF binary

**Output**

Binary files corresponding to ELF sections, processed component description in XML

The component binary splitter tool processes component binaries and creates a separate file for each ELF section. The component XML description is extended by adding a file-backed memory region for each ELF section with the appropriate virtual mapping address, size and access rights. The RIP value is set to the ELF entry point of the component binary.

The resulting processed component description is written to the given output location while the binary section files are written to the specified output path.

<sup>10</sup><https://git.codelabs.ch/?p=muen/mugenhwcfg.git>

<sup>11</sup><https://github.com/roburio/mugenhwcfg-live>

### 5.5.5 Microcode Updates

The `mucfguicode` tool is used to enable Intel processor microcode updates (MCU) on Muen.

**Name**

`mucfguicode`

**Input**

System policy in format source, directory containing Intel microcode updates

**Output**

System policy in format source containing a file-backed microcode memory region. The Intel microcode update blob is copied to the specified output directory

The microcode update tool processes a system policy in format source, extracts the signature of the target processor from the CPUID leaf 1 eax register value and executes the `iucode-tool`<sup>12</sup> for the specified directory containing Intel microcode updates. See the Intel SDM Vol. 3A, "9.11 Microcode Update Facilities" for more information on Intel MCU.

The tool adds a file-backed physical memory for a matching MCU of the given processor. Also, the MCU is copied to the specified output directory with a `.uicode` suffix.

If a physical memory region for MCU already exists, it is removed before further processing. The system policy is left unchanged if the tool does not find an applicable MCU for the target processor.

---

<sup>12</sup><https://gitlab.com/iucode-tool/iucode-tool/-/wikis/home>

Figure 5.1: Build process

# Chapter 6

# Policy Validation

Prior to operate on the policy, any tool outlined in the toolchain section 5.3 checks all required preconditions by running *validator* procedures. For example a tool accessing physical devices via subject logical device references will execute a validator checking such references for validity.

Before the policy is used to generate system structures like sinfo regions, or the command stream for  $\tau_0$ , the expanded policy in format B is validated by executing a comprehensive set of checks. This is done by the `mucfgvalidate` tool outlined in section 5.3.7.

The following sections list the various checks executed by `mucfgvalidate` and the other Muen build tools in the toolchain.

## 6.1 Configuration

The following checks are performed to guarantee correctness of configuration options in the system policy.

- Validate config variable name uniqueness.

- Check that all booleans defined in config contain a valid value.

- Check that all integers defined in config contain a valid value.

- Check that all expression config variable references are valid.

- Check that all integers defined in expressions contain a valid value.

- Check that all booleans defined in expressions contain a valid value.

- Check that all conditional config variable references are valid.

## 6.2 Devices

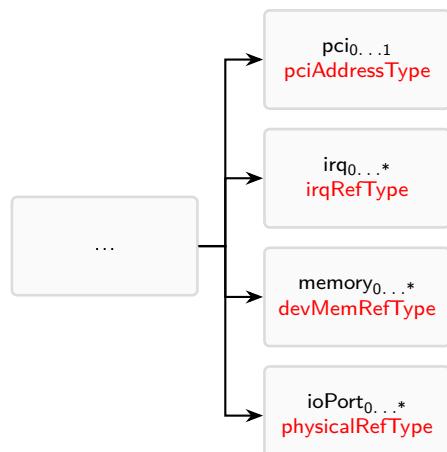

The following checks are performed to guarantee that hardware devices are correctly configured in the system policy.

- Validate that devices referenced by logical devices exist.

- Validate that device names (including device aliases/classes) are unique.

- Validate that all physical IRQs are unique.

- Validate that physical device IRQs referenced by logical IRQs exist.

- Validate that ISA IRQs fulfill their constraints.

- Validate that PCI LSI IRQs fulfill their constraints.

- Validate that PCI MSI IRQs fulfill their constraints.

- Validate that PCI MSI IRQs are consecutive.

- Validate that physical IRQ names are unique per device.

- Validate that all I/O start ports are smaller than end ports.

- Validate that physical I/O ports referenced by logical I/O ports exist.

- Validate that all physical I/O ports are unique.

- Validate that physical I/O port names are unique per device.

- Validate that device memory names are unique per device.

- Validate that device memory referenced by logical device memory exists.

- Validate that PCI device bus, device, function triplets are unique.

- Validate that logical device references of each subject do not refer to the same physical device.

- Validate that PCI device reference bus, device, function triplets are unique per subject.

- Validate that all device references specifying a bus, device, function triplet are references to physical PCI devices.

- Validate that all device references to PCI multi-function devices belong to the same subject and have the same logical device number.

- Validate that all device references not specifying a bus, device, function triplet are references to physical legacy (non-PCI) devices.

- Validate that all logical PCI devices specify bus number zero.

- Validate that all IOMMU memory-mapped IO regions have a size of 4K.

### 6.3 Device Domains

The following checks are performed to guarantee that IOMMU device domains are correctly configured in the system policy.

- Validate that domain device references are unique.

- Validate that no virtual memory regions of a domain overlap.

- Validate that domain memory referenced by subjects is mapped at the same virtual address.

- Validate memory type of physical memory referenced by domains.

- Validate that each device referenced by a device domain is a PCI device.

- Validate that each device domain has a physical PT memory region.

- Validate that each PCI bus has a physical VT-d context memory region.

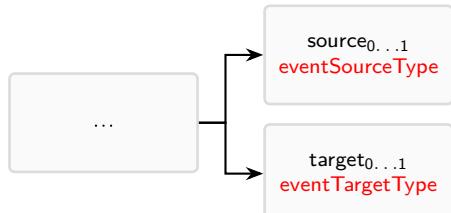

### 6.4 Events

The following checks are performed to guarantee that events are correctly configured in the system policy.

- Check that all physical event names are unique.

- Check that each global event has associated sources and one target.

- Check subject event references.

- Validate that there are no self-references in subject's event notification entries.

- Validate that notification entries switch to a subject running on the same core and in the same scheduling group.

- Validate that target subjects of IPI notification entries run on different logical CPUs.

- Validate that target event IDs as well as logical names are unique.

- Validate that source event IDs as well as logical names are unique per group.

- Check source event ID validity.

- Check that source event IDs of the VMX Exit group are all given or a default is specified.

- Check that self events provide a target action.

- Check that kernel-mode events have an action specified.

- Check that system-related actions are only used with kernel-mode events.

- Check that level-triggered IRQs have a corresponding unmask IRQ event.

## 6.5 Files

The following file-specific checks are performed.

- Check existence of files referenced in XML policy.

- Check if files fit into corresponding memory region.

## 6.6 Hardware

The following checks are performed on the hardware section of the policy.

- Validate that memory regions fit into available hardware memory.

- Validate that no memory blocks overlap.

- Validate that the size of memory blocks is a multiple of page size.

- Validate that PCI config space address and size are specified if PCI devices are present.

- Validate that the hardware provides enough physical CPU cores.

- Validate that the processor CPU sub-elements are correct.

- Validate that at least one I/O APIC device is present.

- Validate that all I/O APICs have a valid source ID capability.

- Validate that at least one and at most eight IOMMU devices are present.

- Validate that all IOMMUs have the AGAW capability set correctly and that multiple IOMMUs specify the same value.

- Validate that all IOMMUs have correct register offset capabilities.

- Check that the hardware contains a system board device providing the expected configuration.

## 6.7 Kernel

The following kernel-specific checks are performed on the policy.

- Validate that all CPU-local data section virtual addresses are equal.

- Validate that all CPU-local BSS section virtual addresses are equal.

- Validate that all global data section virtual addresses are equal and that the expected number of mappings exists.

- Validate that all stack virtual addresses are equal.

- Validate that all crash audit mappings exist and that their virtual addresses are equal.

- Validate that all (if any) microcode update virtual addresses are equal.

- Validate that every kernel has a stack and interrupt stack region mapped and both regions are guarded by unmapped pages below and above.

- Validate that all IOMMU memory-mapped IO regions are consecutive.

- Validate that each active CPU has a memory section.

- Validate that no virtual memory regions of the kernel overlap.

- Validate that the system board is referenced in the kernel logical devices section and that it provides a logical reset port.

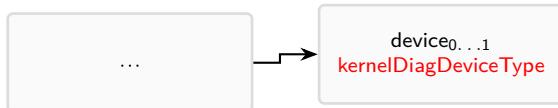

- Validate that the debug console device and its resources matches the kernel diagnostics device specified in the platform section.

## 6.8 Memory

The following checks are performed to verify that the memory is correctly configured in the system policy.

- Validate that a VMXON region exists for every specified kernel.

- Validate size of VMXON regions.

- Validate that VMXON regions are in low-mem.

- Validate that all VMXON regions are consecutive.

- Validate that a VMCS region exists for each declared subject.

- Validate size of VMCS regions.

- Validate that physical memory region names are unique.

- Validate that physical memory referenced by logical memory exists.

- Validate that all physical memory addresses are page aligned.

- Validate that all virtual memory addresses are page aligned.

- Validate that all memory region sizes are multiples of page size.

- Validate kernel or subject entities encoded in physical memory names (e.g. linux|zp or kernel\_0|vmxon).

- Validate that no physical memory regions overlap.

- Validate that an uncached crash audit region is present.

- Validate that there is either zero or exactly one MCU region present.

- Validate that a kernel data region exists for every CPU.

- Validate that a kernel BSS region exists for every CPU.

- Validate that a kernel stack region exists for every CPU.

- Validate that a kernel interrupt stack region exists for every CPU.

- Validate that a kernel PT region exists for every CPU.

- Validate that kernel PT regions are in the first 4G.

- Validate that scheduling info regions are mapped by the kernel running subjects of that scheduling partition. Also verify that the kernel mapping is at the expected virtual location.

- Validate that a subject state memory region with the expected size exists for every subject.

- Validate that a subject interrupts memory region with the expected size exists for every subject.

- Validate that memory of type kernel is only mapped by kernel or Tau0.

- Validate that memory of type system is not mapped by any entity.

- Validate that memory of type 'device' (e.g. device\_rmrr) is only mapped by device domains.

- Validate that subject state memory regions are mapped by the kernel running that subject. Also verify that the kernel mapping is at the expected virtual location.

- Validate that subject interrupts memory regions are mapped by the kernel running that subject. Also verify that the kernel mapping is at the expected virtual location.

- Validate that subject MSR store memory regions are mapped by the kernel running that subject. Also verify that the kernel mapping is at the expected virtual location.

- Validate that subject timed event memory regions are mapped by the kernel running that subject. Also verify that the kernel mapping is at the expected virtual location.

- Validate that subject VMCS regions are mapped by the kernel running that subject. Also verify that the kernel mapping is at the expected virtual location.

- Validate that subject FPU state regions are mapped by the kernel running that subject. Also verify that the kernel mapping is at the expected virtual location.

- Validate that a subject FPU state memory region with the expected size exists for every subject.

- Validate that a subject timed event memory region with the expected size exists for every subject.

- Validate that a subject I/O Bitmap region with the expected size exists for every subject.

- Validate that a subject MSR Bitmap region with the expected size exists for every subject.

- Validate that a subject MSR store memory region exists for each subject that accesses MSR registers not managed by VMCS.

- Validate that a subject pagetable memory region exists for each subject.

- Validate that a scheduling info memory region exists for each scheduling partition.

- Validate that subjects map the scheduling info region of their associated scheduling partition.

- Validate that subject state, timed event and pending interrupts memory regions are only mapped writable by subjects in the same scheduling group or by siblings.

- Validate size of VT-d root table region.

- Validate size of VT-d context table region.

- Validate that a VT-d root table region exists if domains are present.

- Validate that a VT-d interrupt remapping table region exists.

## 6.9 Model Specific Registers (MSR)

The following checks are performed to verify Model Specific Register (MSR) specifications in the system policy.

- Validate that all MSR start addresses are smaller than end addresses.

- Validate that subject MSRs are in the allowed list:

- IA32\_SYSENTER\_CS/ESP/EIP

- IA32\_DEBUGCTL

- IA32\_EFER/STAR/LSTAR/CSTAR/FMASK

- IA32\_FS\_BASE/GS\_BASE/KERNEL\_GS\_BASE

- MSR\_PLATFORM\_INFO

- IA32\_THERM\_STATUS

- IA32\_TEMPERATURE\_TARGET

- IA32\_PACKAGE\_THERM\_STATUS

- MSR\_RAPL\_POWER\_UNIT

- MSR\_PKG\_POWER\_LIMIT

- MSR\_PKG\_ENERGY\_STATUS

- MSR\_DRAM\_ENERGY\_STATUS

- MSR\_PP1\_ENERGY\_STATUS

- MSR\_CONFIG\_TDP\_CONTROL

- IA32\_PM\_ENABLE

- IA32\_HWP\_CAPABILITIES

- IA32\_HWP\_REQUEST

## 6.10 Platform

The following checks are performed to verify the correctness of the platform configuration in the system policy.

- Validate that physical devices referenced by device aliases exist.

- Validate that physical device resources referenced by device aliases exist.

- Validate that physical devices referenced by device classes exist.

- Validate that subject devices that reference an alias only contain resources provided by the device alias.

- Validate that the physical device and resources referenced by the kernel diagnostics device exists.

- Validate that the kernel diagnostics device resources match the requirements of the specified diagnostics type.

## 6.11 Scheduling

The following checks are performed to verify the correctness of the scheduling configuration in the system policy.

- Validate that scheduling partition IDs are unique.

- Validate that scheduling group IDs are unique.

- Validate that each major frame specifies the same number of CPUs.

- Validate that scheduling partitions are scheduled in at least one minor frame and that all minor frame references are on the same logical CPU.

- Validate subject references.

- Validate that subjects are scheduled on the correct logical CPU.

- Validate that subjects are part of exactly one scheduling group.

- Validate that all subjects of a scheduling group are runnable.

- Validate tick counts in major frame.

- Validate that barrier IDs do not exceed barrier count and are unique.

- Validate that barrier sizes do not exceed the number of logical CPUs.

- Validate that the barrier sizes and count of a major frame corresponds to the minor frame synchronization points.

- Validate that minor frame barrier references are valid.

- Validate partition references in minor frames.

## 6.12 Subjects

The following checks are performed to verify the correctness of the subject configuration in the system policy.

- Validate subject name uniqueness.

- Validate subject CPU ID.

- Validate uniqueness of global subject IDs.

- Validate per-CPU uniqueness of local subject IDs.

- Validate memory types of memory mappings (ie. allow access by subjects).

- Validate that no subject references an IOMMU device.

- Validate that all subjects are runnable, i.e. referenced in a scheduling group.

- Validate that subject scheduling group IDs match values as determined by the scheduling plan and handover events.

- Validate that logical names of subject memory regions are unique.

- Validate that logical names of subject devices are unique.

- Validate that IRQ vector numbers of PCI device references with MSI enabled are consecutive.

- Validate that logical names of subject unmask IRQ events conform to the naming scheme (unmask\_irq\_\$IRQNR) and that the unmask number matches the physical IRQ.

- Validate that no virtual memory regions of a subject overlap.

- Validate that multiple initramfs regions are consecutive.

- Validate that no subject has write access to the crash audit region.

- Validate that subject device mmconf mappings are correct.

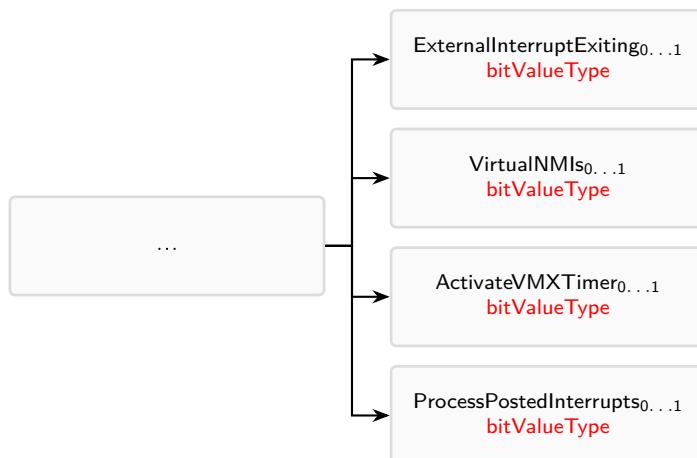

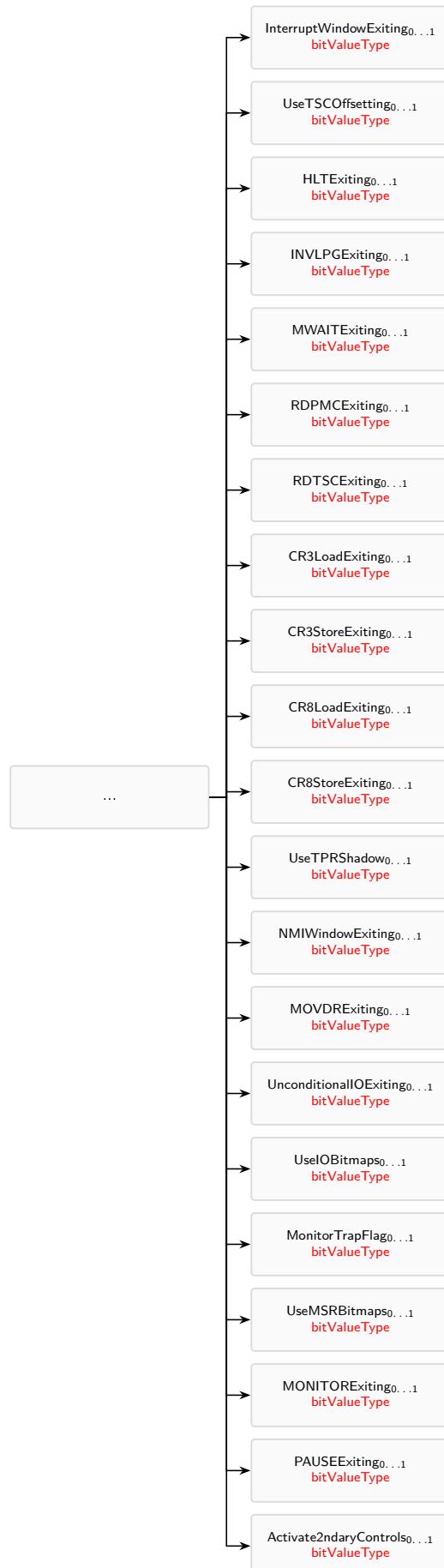

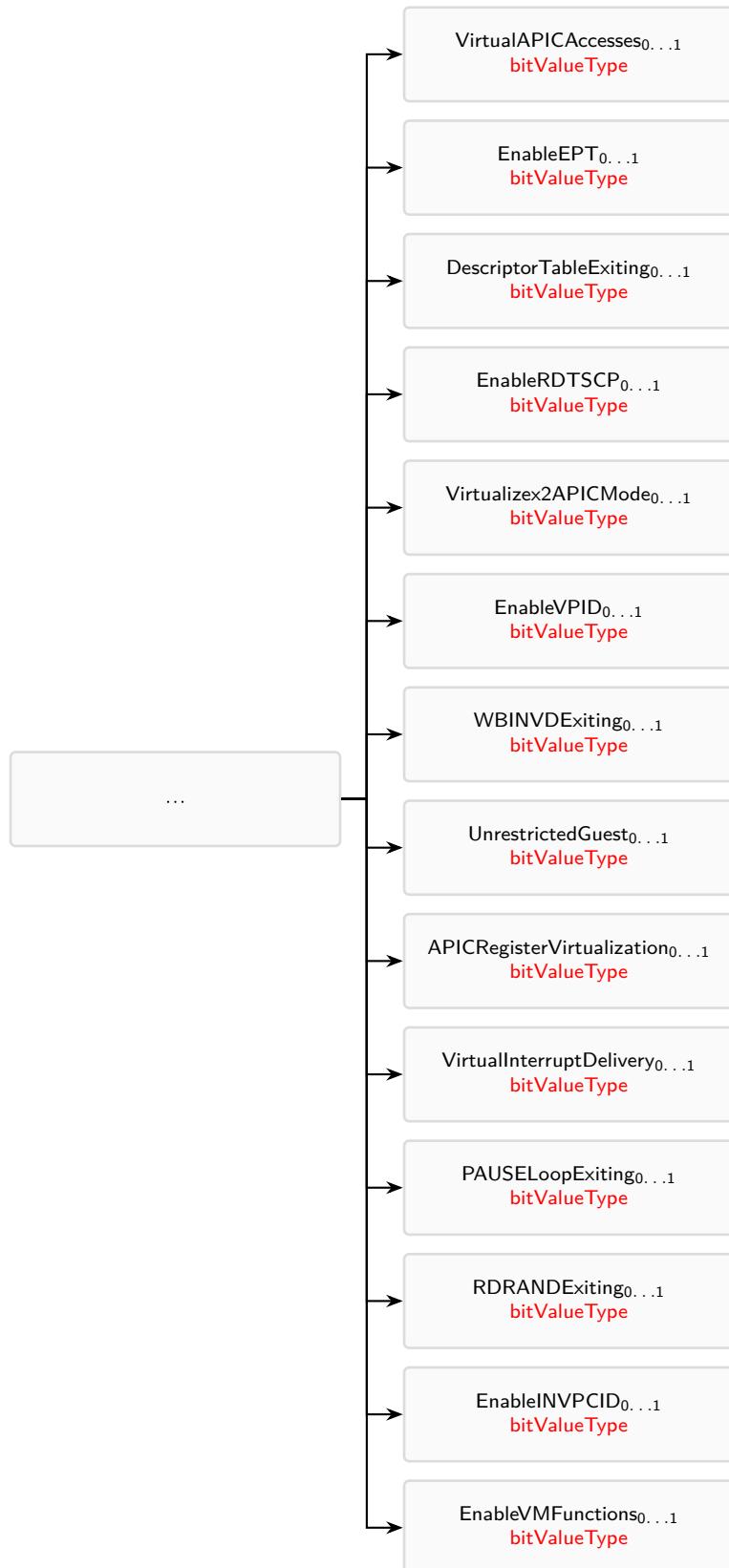

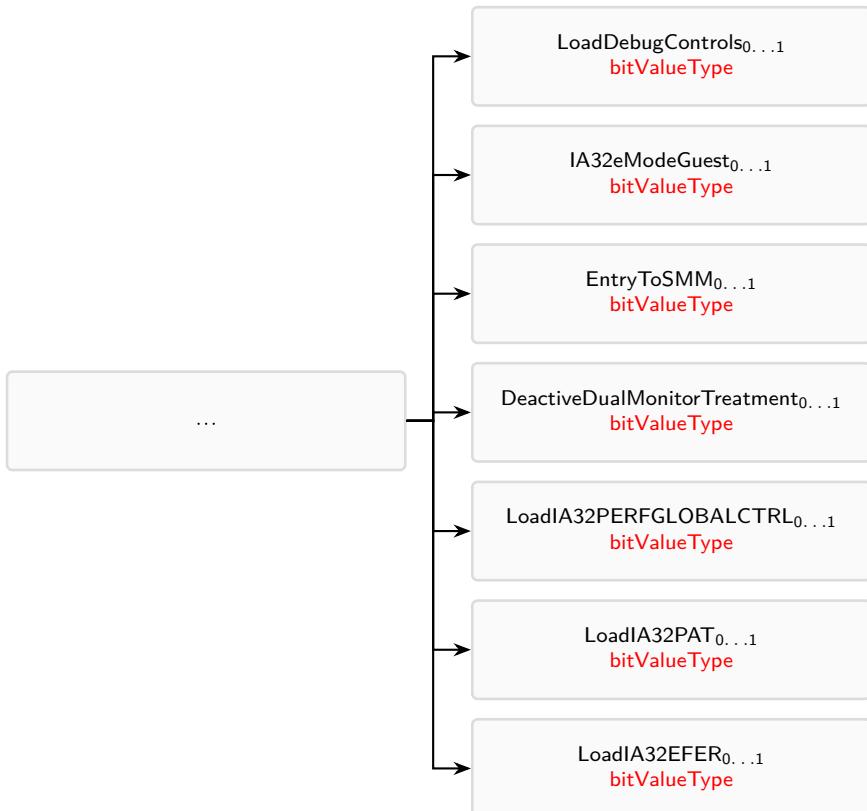

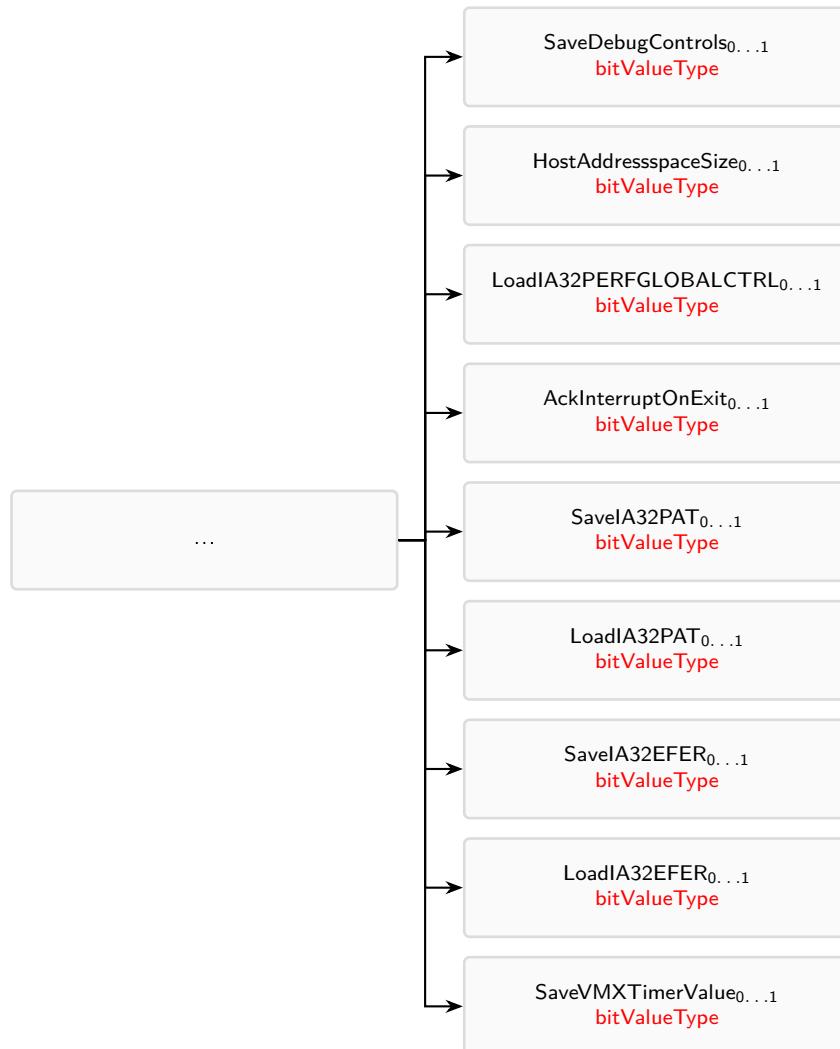

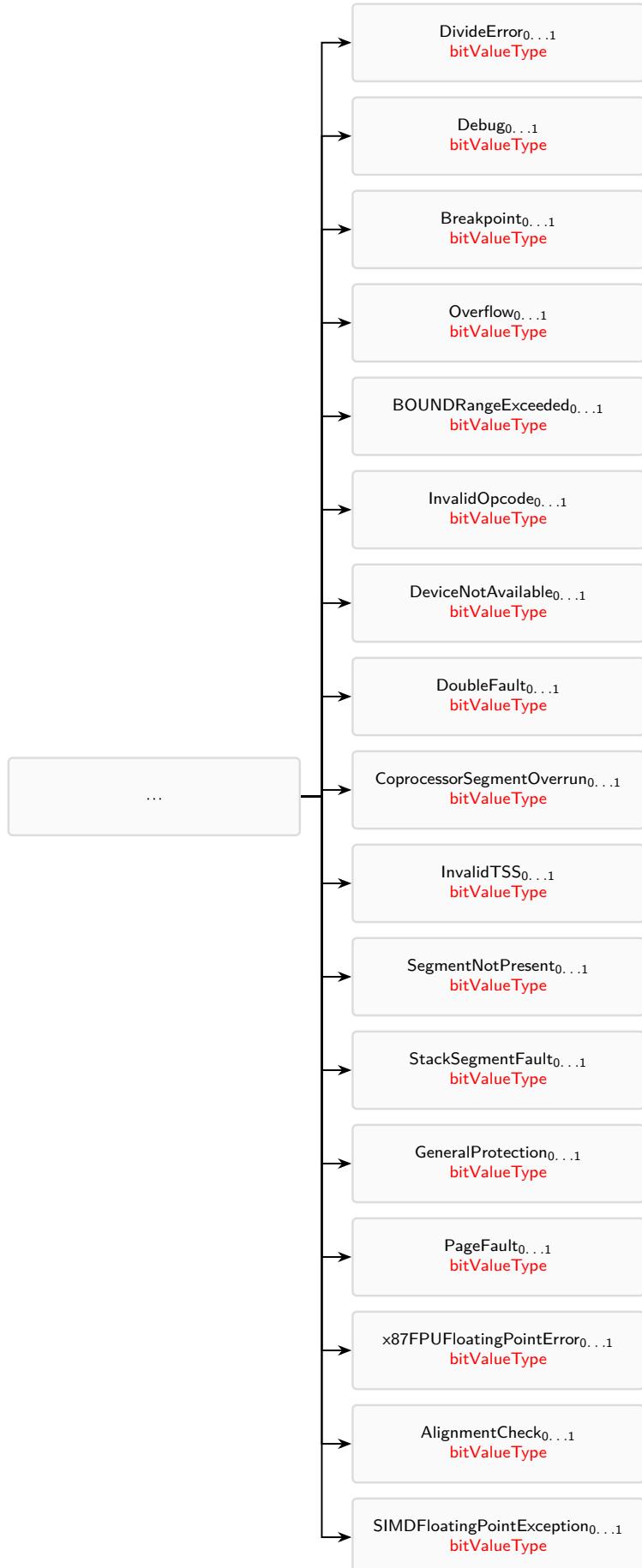

- Validate that the VMX controls conform to the checks specified in Intel SDM Vol. 3C, "26.2.1 Checks on VMX Controls".

- Validate that the Pin-Based VM-Execution controls meet the requirements for the execution of Muen.

- Validate that the Processor-Based VM-Execution Controls meet the requirements for the execution of Muen.

- Validate that the secondary Processor-Based VM-Execution Controls meet the requirements for the execution of Muen.

- Validate that the VM-Exit Controls meet the requirements for the execution of Muen.

- Validate that the VM-Entry Controls meet the requirements for the execution of Muen.

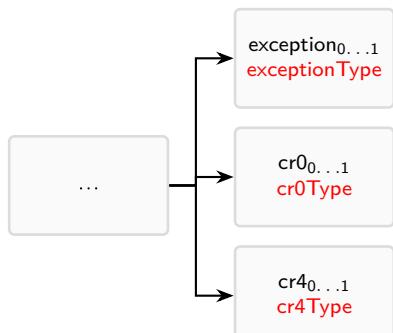

- Validate that the VMX CR0 guest/host masks meet the requirements for the execution of Muen.

- Validate that the VMX CR4 guest/host masks meet the requirements for the execution of Muen.

- Validate that the VMX Exception bitmap meet the requirements for the execution of Muen.

# Chapter 7

## Policy Structure

### 7.1 Policy Schema Documentation

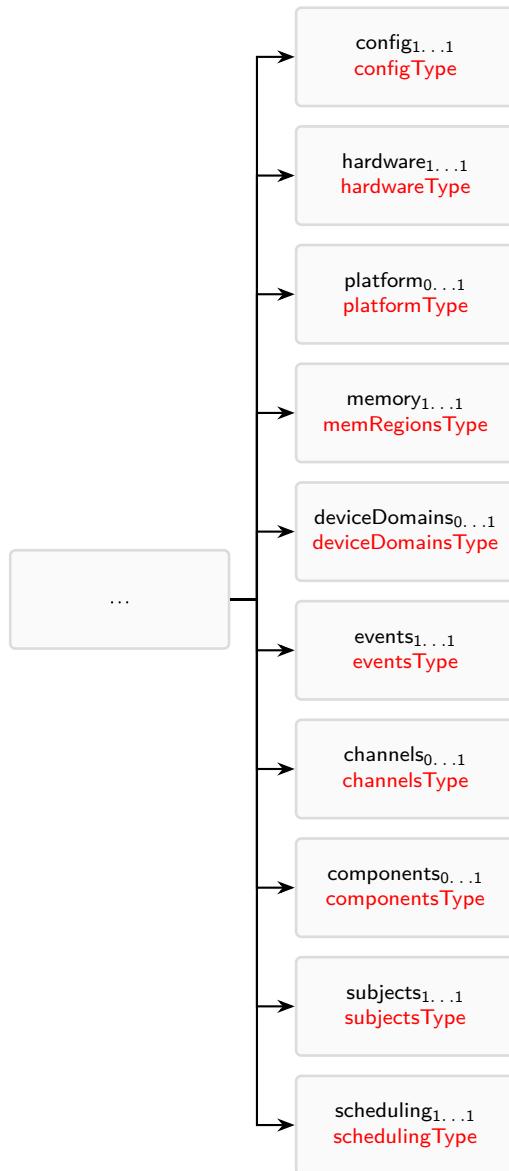

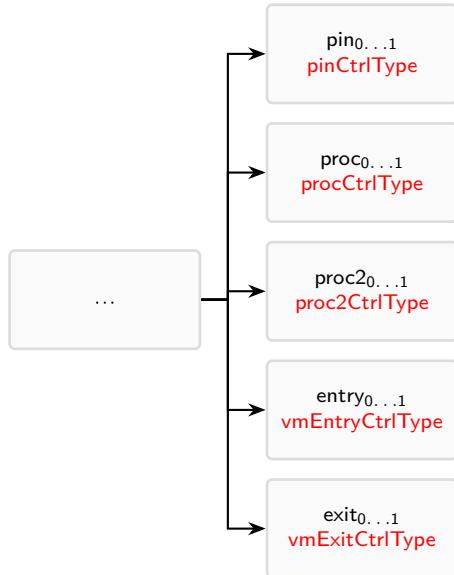

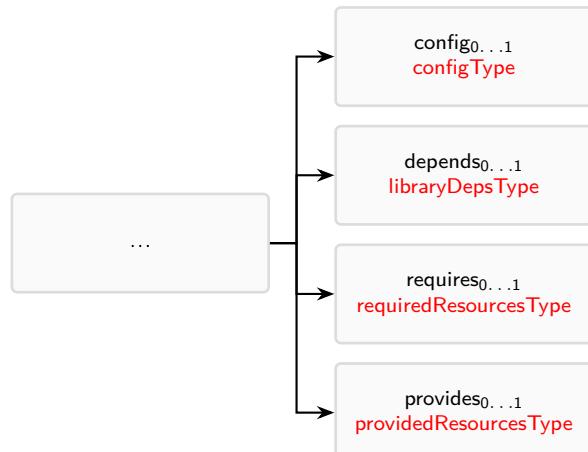

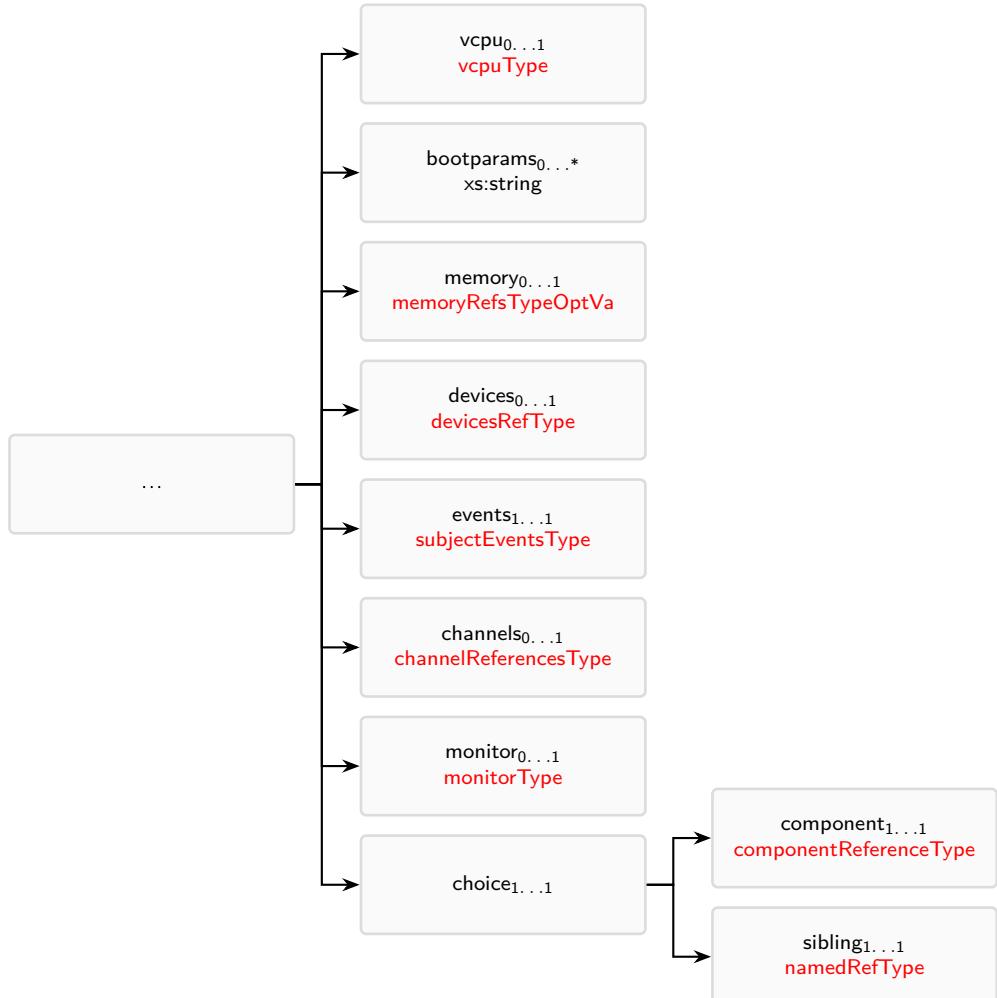

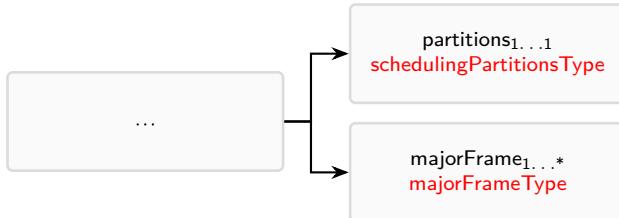

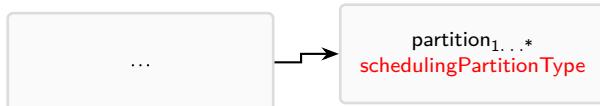

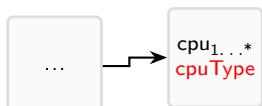

#### 7.1.1 systemType

A Muen system policy specifies all hardware resources such as physical memory, devices, CPU time, etc and how these resources are accessed by the separation kernel, the subjects and devices.

The `system` section is the top-level element in the Muen system policy. It contains various sub-elements which specify all aspects of a concrete system.

This is the *source format* of the Muen system policy. It allows for abstractions, such as channels, which are broken down into their constituent parts by the toolchain in format A and B accordingly.

See line 3 and following in listing 8.1 on page 105 for an annotated system policy example.

## Structure

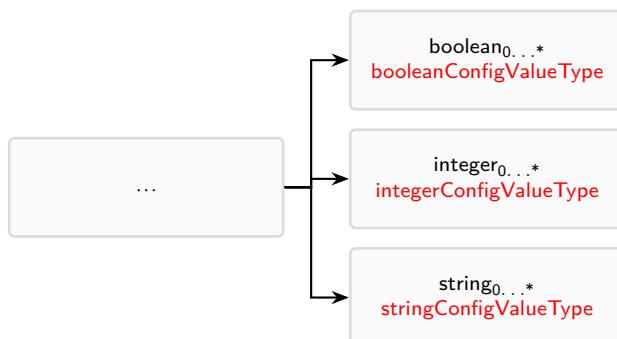

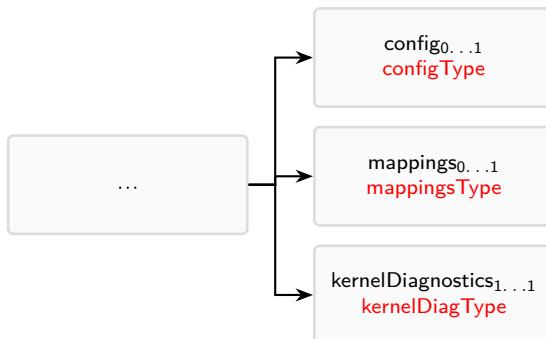

### 7.1.2 configType

The purpose of a config section is to specify configuration values which parameterize a system or a component. It allows to declare boolean, string and integer values. The following sections in the system policy provide support for configuration values:

- System

- Platform

- Component

During the build process, configuration values provided by the platform are merged into the global system configuration. Component configuration values allow the parameterization of component-local functionality.

Besides component parameterization, configuration options can be used in `if` conditionals, as shown in the following example.

```

1  <if variable="xhcidbg_enabled" value="true">

2  ...

3  </if>

```

If the type of the referenced variable is 'string' the comparison is case-sensitive. A second use case is XML attribute value expansion as follows:

```

1  <channel name="debuglog" size="$logchannel_size"/>

```

The `size` attribute value is not specified directly, but parameterized via an integer configuration option.

See line 17 in listing 8.1 for an example config section.

## Structure

### 7.1.3 booleanConfigValueType

Configuration option for values in boolean format.

#### Attributes

| Name  | Type        | Use                                            |

|-------|-------------|------------------------------------------------|

| name  | nameType    | optional<br>Name of the configuration option.  |

| value | booleanType | optional<br>Value of the configuration option. |

### 7.1.4 nameType

**Base:** xs:string

The `nameType` is used to give (unique) names to elements.

#### Restrictions

minimal length = 1, maximal length = 63

### 7.1.5 booleanType

**Base:** xs:string

Boolean type.

#### Restrictions

values:

- true

- false

### 7.1.6 integerConfigValueType

Configuration option for values in integer format.

#### Attributes

| Name  | Type       | Use                                            |

|-------|------------|------------------------------------------------|

| name  | nameType   | optional<br>Name of the configuration option.  |

| value | xs:integer | optional<br>Value of the configuration option. |

### 7.1.7 stringConfigValueType

Configuration option for values in string format.

#### Attributes

| Name  | Type      | Use                                            |

|-------|-----------|------------------------------------------------|

| name  | nameType  | optional<br>Name of the configuration option.  |

| value | xs:string | optional<br>Value of the configuration option. |

### 7.1.8 hardwareType

Systems running the Muen SK perform static resource allocation at integration time. This means that all available hardware resources of a target machine must be defined in the system policy in order for these resources to be allocated to subjects.

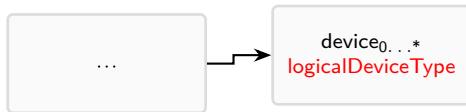

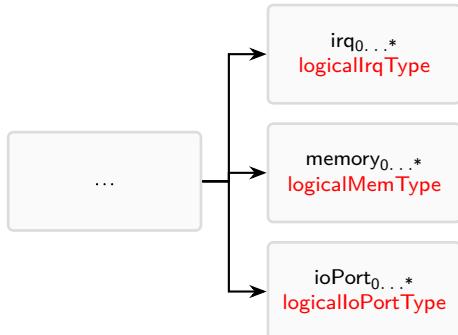

The hardware element is the top-level element of the hardware specification in the system policy. Information provided by a hardware description includes the amount of available physical memory blocks including reserved memory regions (RMRR), the number of physical CPU cores and hardware device resources.

The Muen toolchain provides a handy tool to automate the cumbersome process of gathering hardware resource data from a running Linux system: mugenhwcfg<sup>1</sup>.

See line 81 in listing 8.1 for an example hardware section.

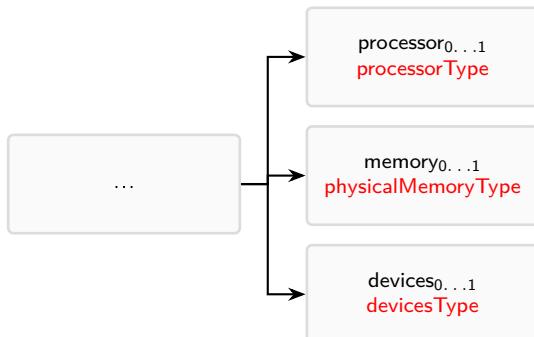

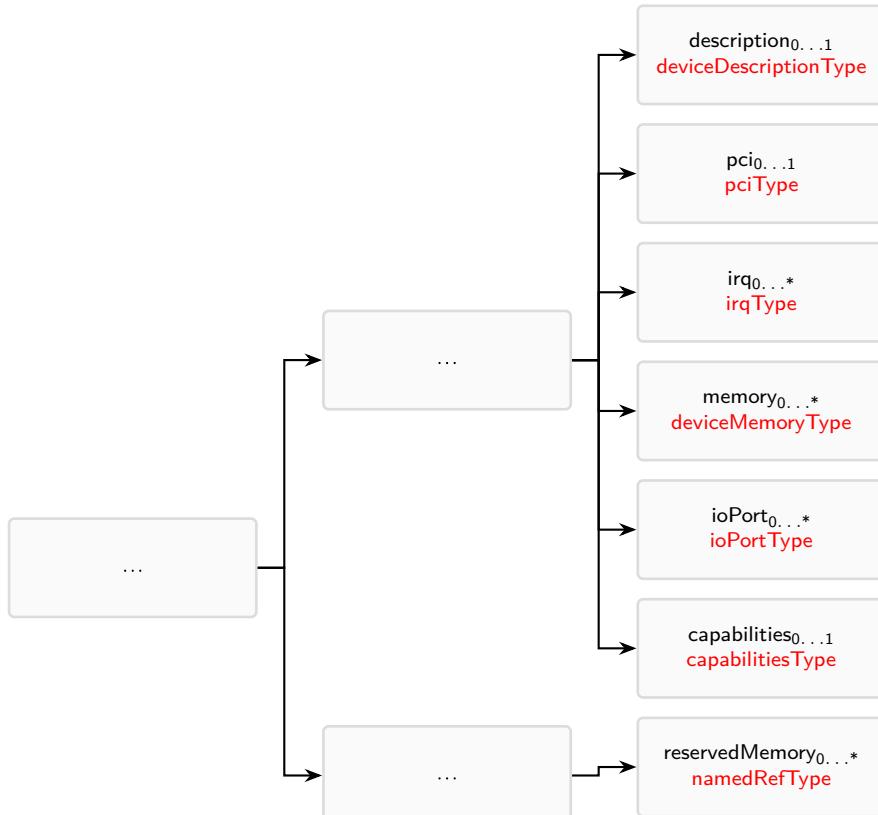

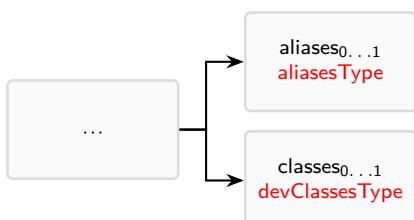

#### Structure

### 7.1.9 processorType

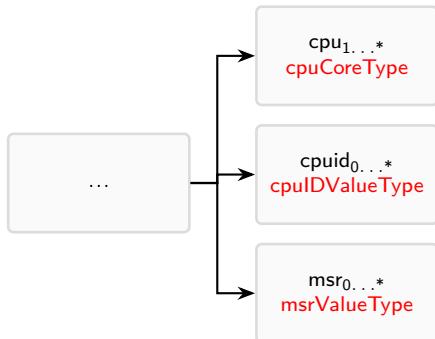

The processor element specifies the number of CPU cores, the processor speed in kHz and the Intel VMX preemption timer rate.

Since Intel CPUs can have arbitrary APIC identifiers, the APIC IDs of all physical CPUs are enumerated here. The APIC ID is required for interrupt and IPI routing.

<sup>1</sup><https://git.codelabs.ch/?p=muen/mugenhwcfg.git>

The processor element also lists register values for all CPUID leaves of the hardware target, and some MSR values of interest.

See line 100 in listing 8.1 for an example processor element. The `cpu` elements must fulfill the following constraints to be valid:

- A node exists for every physical core of the system

- The optional `cpuid` attribute of all elements must be consecutive

- If specified, a node with `cpuid` value 0 must exist

- A node with `apicId` value 0 must exist and, if specified, it must have a `cpuid` value within the active CPU range, i.e. the BSP is part of the system scheduling plan

- All `apicId` attributes must have even numbers

## Attributes

| Name                      | Type                            | Use                                                                                                                                                                                                                          |

|---------------------------|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <code>cpuCores</code>     | <code>xs:positiveInteger</code> | required<br>Number of available CPU cores. Note that this value designates physical, hardware cores, not Hyper-Threading (HT) threads. HT is disabled on Muen.                                                               |

| <code>speed</code>        | <code>xs:positiveInteger</code> | required<br>Tick rate of CPU cores in kHz.                                                                                                                                                                                   |

| <code>vmxTimerRate</code> | <code>vmxTimerRateType</code>   | required<br>The VMX-preemption timer counts down at a rate proportional to that of the timestamp counter (TSC). This value specifies this proportion, see Intel SDM Vol. 3C, "25.5.1 VMX-Preemption Timer" for more details. |

## Structure

### 7.1.10 `cpuCoreType`

Specification of one physical CPU core.

## Attributes